## Combining P2 and RDL to build Dataflow Hardware Programs

<http://ramp.eecs.berkeley.edu>

Greg Glibeling, Nathan Burkhart and Andrew Shultz

{gdgib, nburkhart, alshultz}@berkeley.edu

5/1/2006

12/21/2006      Combining P2 and RDL      1

## Outline

- RAMP Architecture & Target Model

- Tools & Toolflow

- RAMP Description Language

- P2

- Status & Future Work

12/21/2006      Combining P2 and RDL      2

## RAMP Architecture

- Target

- The system being emulated

- Actually only a model of the system being emulated

- Can be a cycle accurate model

- Must conform to the RAMP target model

- Host

- The system doing the emulation

- May include multiple platforms

- Hardware – BEE2, XUP, CaLinx2

- Emulation – Matlab, ModelSim

- Software – C++, Java

12/21/2006      Combining P2 and RDL      3

## RAMP Target Model (1)

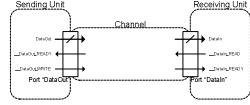

- Units communicate over channels

- Units

- Implemented in a “host” language

- Smaller than a DB Op

- Channels

- Unidirectional

- Point-to-point

- FIFO semantics

- Similar to the Exchange operator from Volcano

12/21/2006      Combining P2 and RDL      4

## RAMP Target Model (2)

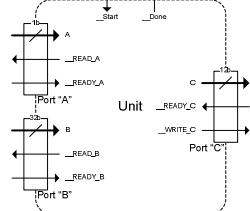

- Transaction style unit semantics

- Read 0/1 messages from each input

- Perform some action

- Write 0/1 messages to each output

- Units must be latency insensitive

- This affects the way SHIPs are coded

12/21/2006      Combining P2 and RDL      5

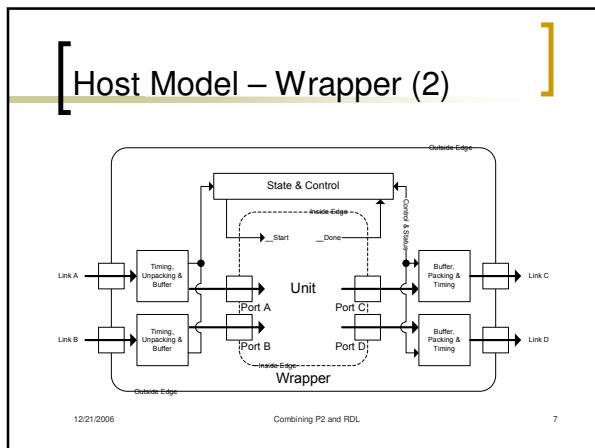

## Target Model - Units

- Inside edge

- Ports connect units to channels

- FIFO signaling

- Hardware or Software

- Target cycle control

- \_\_Start

- \_\_Done

- Allows for variable timing, and timing accurate simulation

12/21/2006      Combining P2 and RDL      6

## RDL (3)

Example RDL here

12/21/2006      Combining P2 and RDL      13

## A FLEET in RDL (1)

12/21/2006      Combining P2 and RDL      14

## State of the Project

- Working hardware implementation!

- Compiled RDL to Verilog

- Tested on CaLinx2, XUP, Digilent S3 and ModelSim SE

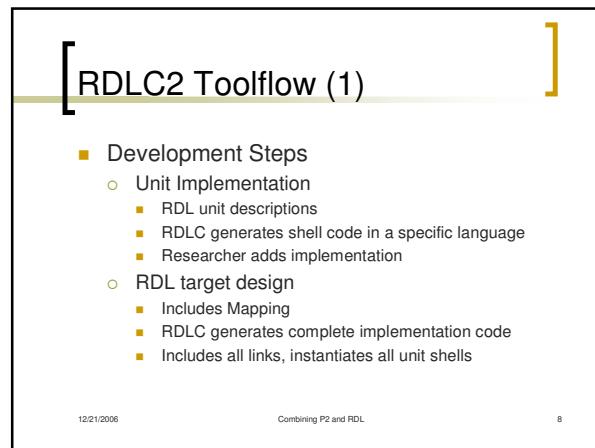

- RDL & RDL Compiler

- RDLC2 is stable

- Working compiler, written in java

- 125,000 lines of code

- Definitely going to get cleaned up

12/21/2006      Combining P2 and RDL      15

## Future Work (1)

- RDL & RDLC Features

- Language Features

- Generated code and compile time parameters

- Support for expressions and better parameters

- Languages, platforms, links

- Debugging automation

- Documentation

- Architecture, Language & Compiler Technical Report

- Complete compiler internals documentation

- Example and Tutorials

12/21/2006      Combining P2 and RDL      16

## Future Work (2)

- Stuff

12/21/2006      Combining P2 and RDL      17